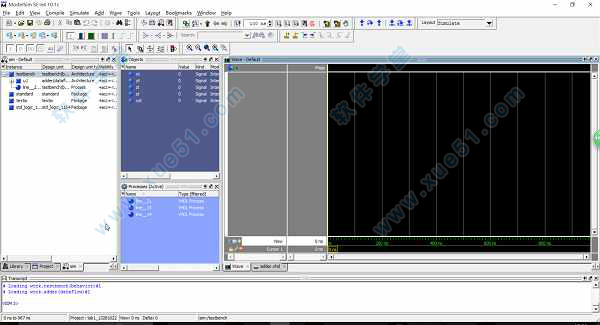

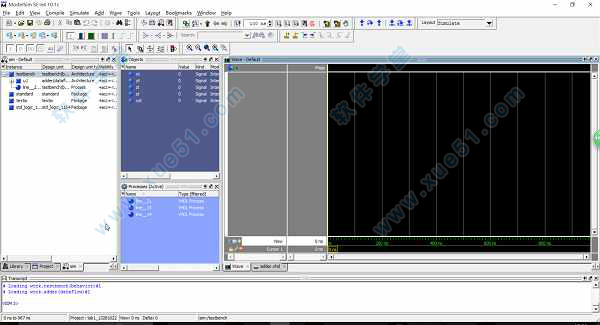

modelsim10.1是一款业界最为优秀的HDL语言

仿真软件,适用于工业设计、教学领域,使用环境非常的友好。由非常知名的Model公司进行研发推出,为用户提供了友好的仿真环境,并且支持对VHDL、Verilog软件的混合仿真,还可将整个程序分成几步进行执行,这样设计者就可以进行观看下一步需要进行执行的语句,也可对当前的值进行查看,包括了这Dataflow窗口进行查看您的需要的模块状态的输出、输入的变化等,使用的范围广。该软件集成了性能分析、波形比较、代码覆盖、数据流ChaseX、Signal Spy、虚拟对象Virtual Object、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能,可以很好的帮助用户进行HDL语言的仿真设计。本站提供

modelsim10.1c破解版下载端口,欢迎有需要的朋友免费下载体验。

功能介绍

1、RTL和门级优化,本地编译结构,编译仿真速度快,跨平台跨版本仿真。

2、单内核VHDL和Verilog混合仿真。

3、源代码模版和助手,项目管理。

4、集成了性能分析、波形比较、代码覆盖、数据流ChaseX、Signal Spy、虚拟对象Virtual Object、Memory窗口、Assertion窗口、源码窗口显示信号值、信号条件断点等众多调试功能。

5、C和Tcl/Tk接口,C调试。

6、对SystemC的直接支持,和HDL任意混合。

7、支持SystemVerilog的设计功能。

8、对系统级描述语言的最全面支持,SystemVerilog,SystemC,PSL。

9、ASIC Sign off。

10、可以单独或同时进行行为(behavioral)、RTL级、和门级(gate-level)的代码。

软件特色

1、Mentor Graphics公司,电子硬件和软件设计解决方案的全球领导者,提供的产品和服务,发布了版本10.4,是一个VHDL,Verilog验证和仿真工具,基于混合语言设计。

2、Mentor Graphics是结合单核模拟器第一(SKS)技术提供了一个统一的调试环境为Verilog,VHDL,和SystemC。

3、行业领先的组合,原生SKS性能最好的集成调试和分析环境使ASIC和FPGA的设计选择的模拟器。行业中最好的标准和平台支持使得在大多数流程和工具流中易于采用。

4、指导图形是电子设计自动化(EDA)的技术领先者,提供软件和硬件设计解决方案,使公司能够更快更有效地开发更好的电子产品。

5、该公司提供创新的产品和解决方案,帮助工程师克服在日益复杂的板和芯片设计领域所面临的设计挑战。导师图形拥有最广泛的行业组合中最好的一流产品,是唯一的EDA公司与嵌入式软件解决方案。

安装教程

1、解压modelsim 10.1c安装包,双击“modelsim-win64-10.1c-se.exe”开始安装的第一步。

2、可直接默认跳过,并且点击“Next”。

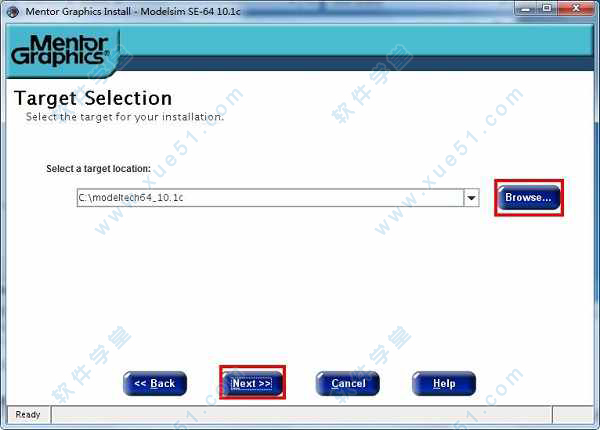

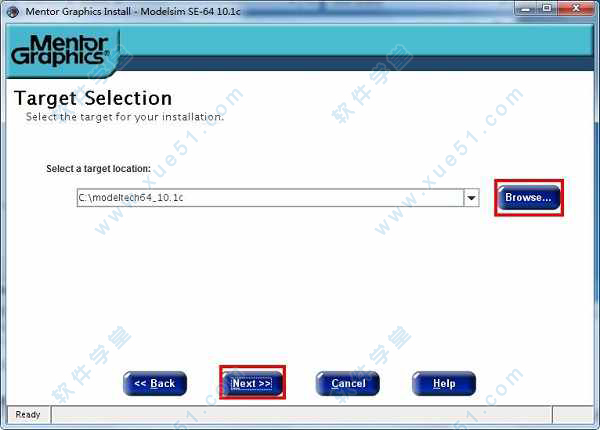

3、选择软件的安装路径,可直接默认“Next”跳过设置,也可点击“BROWSE”自定义程序的安装路径。

4、如果选择默认路径的用户,系统机会提示“本机没有该文件夹,是否自动创建该文件夹”,直接点击“YES”允许程序自己创建文件夹。

5、显示相关的许可证协议,这里具体介绍了相关许可证的安装需要的注意事项和相关信息。直接点击“Agree”直接安装。

6、开始正式的安装,安装到50%的时候,程序会弹出窗口,并询问是否要创建桌面快捷方法,这里建议点击“Yse”。

7、再次弹出窗口,并提示,是否将Modelsim的路径添加到你的路径(Start菜单吧)里面,建议点击“Yse”。

8、提示是否添加硬件安全钥匙驱动,并解释相关的驱动信息,这里建议点击“No”。

9、点击“DONe”完成安装并退出安装界面。

破解教程

一、将安装包内的“MentorKG.exe”和“patch_dll.bat”复制到软件的安装目录的win64或wiin32文件夹下复制说明:

1、默认路径为“C:\modeltech64_10.1c\win64”。

2、如果用户修改过安装路径,但是却忘记的,建议:鼠标右键桌面快捷启动项,然后点击“打开文件位置”即可直接定位到安装目录中。

二、鼠标右键点击“patch_dll.bat”,然后点击“用记事本打开该文件”,然后将里面的内容修改为:

attrib -r C:\modeltech64_10.1c\win64\mgls.dll

pause

attrib +r C:\modeltech64_10.1c\win64\mgls.dll

pause

输入完成,点击文件-保存。

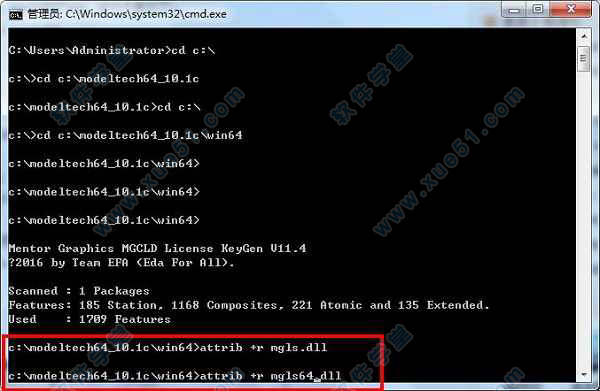

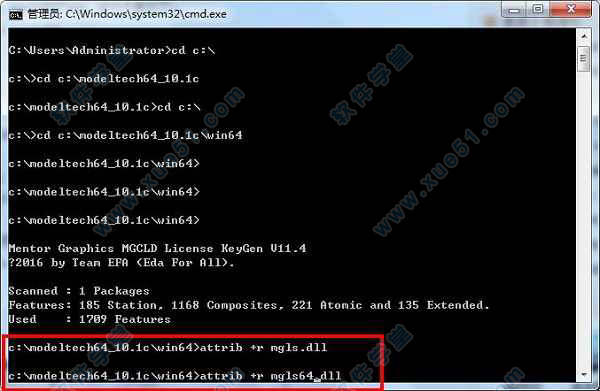

三、保存后,打开patch_dll,执行第一条指令,也就是按一次“Enter”键,之后不要关闭,也不要去管他四、使用命令提示符来执行,win+r运行cmd,再次打开一次cmd窗口,输入以下命令:

1、cd c:\(如果用户安装路径是c盘就定义C,d盘就定义D)完成按enter键。

2、CD c:\modeltech64_10.1c/win64(同样安装路径根据用户自定义的路径决定)同样完成按enter键。

3、连续输入以下命令:

attrib -r mgls.dll

attrib -r mgls64.dll

MentorKG.exe -patch .\(这里一定要注意空格)。

完成按enter键。

4、出现如下信息,等待1-3分钟即会弹出相应的注册文件,点击文件-另存为,将其保存在主目录中,默认为C:\modeltech64_10.1c。

5、继续输入:

attrib +r mgls.dll

attrib +r mgls64.dll

五、再次运行刚才打开的patch_dll文件,继续按Enter键执行下一条命令。

六、右击我的电脑或计算机—属性-高级系统设置—环境变量。

七、点击在系统变量的新建,第一个格写:MGLS_LICENSE_FILE,第二个写你刚才license.txt保存的地址(我的是C:\modeltech64-10.1c\LICENSE.TXT)连续选确定退出。

八、完成程序的破解,用户可完全免费使用modelsim 10.1c啦。

常见问题

1、直接将用VerilogHDL编写的128分频器程序count128.v设置为工程的顶层设计文件,编译失败?快速建立了一个只有一个器件的电路图文件:Msim.bdf,将输入输出信号直接引出来,并将其设为顶层文件,编译通过。

2、编译通过后进行仿真,仿真失败?原因是:

已经设定仿真语言为Verilog HDL。

解决方法:

用手工重新写了一段Verilog HDL语言的顶层设计文件MSim.V。编译通过,并且仿真正常。

3、波形加载慢的问题解决办法?

方法一

先仿真1ms,然后zoom full一次,在此基础上再跑1ms,再zoom full,依此类推跑到10ms,这时再zoom full就很快地完成了。我猜原因是前面的9次zoomfull建立了一些缓存数据,以供第10次使用,所以变快了。

方法二

变化频率最大的信号删除掉,通常情况下,变化频率最大的信号是时钟信号,如果一定要保留,那么可以将该信号的format设为literal,或者event,如果format是logic,将严重拖慢画波形的速度。设置的方法是在波形信号处点击右键,选择format->literal。

注意事项

1、电脑的用户名不能为中文。

2、安装路径不能出现中文和空格,只能有数字、英文字母和下划线"_"组成。

3、若计算机还需要使用Altera 6.4a (Quartus II 9.0),可不需做任何额外的设定,SE 6.3g会自动抓到这个系统变量,并使用这个license file;反之亦然。

Modelsim SE-64 10.6d

764MB

简体中文

Modelsim SE-64 10.6d

764MB

简体中文

modelsim se 2019.2最新64位

851MB

简体中文

modelsim se 2019.2最新64位

851MB

简体中文

modelsim 10.4 64位v1.0

495MB

简体中文

modelsim 10.4 64位v1.0

495MB

简体中文

modelsim 64位

502MB

简体中文

modelsim 64位

502MB

简体中文

0条评论